# **ADVANCE PROGRAM**

## **2020 IEEE** INTERNATIONAL SOLID-STATE CIRCUITS CONFERENCE

FEBRUARY 16, 17, 18, 19, 20

**CONFERENCE THEME:**

INTEGRATED CIRCUITS FRA POWF RING THF ΔΙ

SAN FRANCISCO **MARRIOTT MARQUIS HOTEL**

> NEW EAR 91 HIGHLIGHTED CHIP RELEASES

Power Management for Future SoCs; Sensors for Health <u>ML Processors; Electrical/Optical Transceiver</u>

**SHORT-GOURSE:** CIRCUIT DESIGN IN ADVANCED CMOS

FORUMS: mm-Wave 5G; ML as Killer App

Capacitive Sensor Interfaces; Wireless Transceiver Circuits/Architectures (2G to 5G); Understand/Evaluate DL Processor LS: INTEGRATED TRANSFORMERS; DCDC CONVERTERS; WEARABLE/IMPLANTABLE SENSING; NONVOLATILE MEMORIES (MRAM RRAM, PRAM); TIME-INTERLEAVED ADCS; DIGITAL FRACTIONAL-N PHASED LOCKED LOOP; LOW-DROPOUT INTEGRATED REGULATORS; **2 EVENING EVENTS:** Graduate Student Research in Progress; Rising Stars 2020

EEE SOLID-STATE CIRCUITS SOCIETY

## **ISSCC VISION STATEMENT**

The International Solid-State Circuits Conference is the foremost global forum for presentation of advances in solid-state circuits and systems-on-a-chip. The Conference offers a unique opportunity for engineers working at the cutting edge of IC design and application to maintain technical currency, and to network with leading experts.

## **CONFERENCE TECHNICAL HIGHLIGHTS**

On Sunday, February 16th, the day before the official opening of the Conference, ISSCC 2020 offers:

- A choice of up to 4 of a total of 10 Tutorials, or

- A choice of 1 of 2 all-day Advanced-Circuit-Design Forums

The 90-minute tutorials offer background information and a review of the basics in specific circuit- and system-design topics. In the all-day Advanced-Circuit-Design Forums, leading experts present state-of-the-art design strategies in a workshop-like format. The Forums are targeted at designers experienced in the technical field.

On Sunday evening, there are two events: A WiC Workshop on "Rising Stars 2020" will be offered starting at 4:00 pm. In addition, the Student-Research Preview, featuring ??? ninety-second introductory presentations followed by a poster session from selected graduate-student researchers from around the world will begin at 7:30 pm. Introductory remarks at the Preview will be provided by a distinguished member of the solid-state circuit community, Tadahiro Kuroda, Professor, University of Tokyo,

On Monday, February 17th, ISSCC 2020 at 8:30 am offers four plenary papers on the theme: "Integrated Circuits Powering the AI ERA". On Monday at 1:30 pm, there begin five parallel technical sessions, followed by a Social Hour at 5:15 pm open to all ISSCC attendees. The Social Hour, held in conjunction with Book Displays and Author Interviews, will also include a Demonstration Session, featuring posters and live demonstrations of selected papers from industry and academia. On Monday evening there is one event. At 8:00 pm "Industry Showcase" will feature short presentations as well as interactive demonstrations where attendees can have a hands-on experience with each featured innovation

On Tuesday, February 18th, there are five parallel technical sessions, both morning and afternoon. A Social Hour open to all ISSCC attendees will follow. The Social Hour, held in conjunction with Book Displays and Author Interviews, will also include a second Demonstration Session. Tuesday evening includes two events, entitled "Quiz Show: "The Smartest Designer in the Universe" and "Open-Source Hardware Revolution".

On Wednesday, February 19th, there will be five parallel technical sessions, both morning and afternoon, followed by Author Interviews.

On Thursday, February 20th, ISSCC offers a choice of five all-day events: • A Short Course entitled: "Circuit Design in Advanced CMOS Technologies — Considerations and Solutions " • Four Advanced-Circuit-Design Forums entitled: "Machine Learning Processors: From High Performance Applications to Architectures and Benchmarking"

"Cutting Edge Advances in Electrical and Optical Transceiver Technologies" "Power Management as an Enabler of Future SoCs" "Sensors for Health"

This year, again, there is an option which allows an attendee to sample parts of all 5 Thursday offerings. Registration for educational events on Sunday and Thursday will be filled on a first-come first-served basis. Use of the ISSCC Web-Registration Site (http://www.isscc.org) is strongly encouraged. Registrants will be provided with immediate confirmation on registration for the Conference, Tutorials, Forums, and the Short Course.

## Need Additional Information? Go to: www.isscc.org

## **TABLE OF CONTENTS**

| Tutoria                 | <b>is</b> 4                                                                                                   | -8 |

|-------------------------|---------------------------------------------------------------------------------------------------------------|----|

|                         | FORUMS                                                                                                        |    |

| F1                      | Millimeter-Wave 5G: From Soup to Nuts and Bolts                                                               | .9 |

| F2                      | ML at the Extreme Edge: Machine Learning as the Killer IoT App                                                | 0  |

|                         | EVENING EVENTS                                                                                                |    |

| EE1<br>EE2              | Student Research Preview: Short Presentations with Poster Session                                             | 1  |

| LLZ                     |                                                                                                               | 0  |

|                         | PAPER SESSIONS                                                                                                | _  |

| 1                       | Plenary14-1                                                                                                   | 5  |

| 2                       | Processors                                                                                                    |    |

| 3                       | Analog Techniques I                                                                                           |    |

| 4                       | mm-Wave Wireless for Communication & Radar                                                                    |    |

| 5                       | Imagers and ToF Sensors                                                                                       |    |

| 6                       | Ultra-High-Speed Wireline                                                                                     |    |

| Demon                   | stration Session 1                                                                                            | !1 |

| <b>FF2</b>              | EVENING EVENTS                                                                                                | 50 |

| EE3                     | Industry Showcase                                                                                             | 2  |

|                         | PAPER SESSIONS                                                                                                |    |

| 7                       | High-Performance Machine Learning                                                                             |    |

| 8                       | Highlighted Chip Releases                                                                                     | 4  |

| 9                       | Noise-Shaping ADCs                                                                                            |    |

| 10                      | High-Performance Transceivers                                                                                 |    |

| 11                      | DC-DC Converters                                                                                              | !/ |

| 12                      | Advanced Optical Communication Circuits                                                                       |    |

| 13                      | Non-Volatile Memories                                                                                         |    |

| 14                      | Low-Power Machine Learning                                                                                    |    |

| 15                      | SRAM & Compute-In-Memory                                                                                      |    |

| 16<br>17                | Nyquist & VCO-Based ADCs                                                                                      | 12 |

| 18                      | GaN & Isolated Power Conversion                                                                               |    |

| 19                      | CRYO-CMOS for Quantum Technologies                                                                            | 14 |

| 20                      | Low-Power Circuits for IoT & Health                                                                           | 10 |

|                         | istration Session 2                                                                                           |    |

|                         |                                                                                                               |    |

| Confer                  | ence Timetable                                                                                                | 9  |

|                         | EVENING EVENTS                                                                                                |    |

| EE4<br>EE5              | Quiz Show: "The Smartest Designer in the Universe"4<br>Is an Open-Source Hardware Revolution on the Horizon?4 | 0  |

| EEO                     | PAPER SESSIONS                                                                                                | U  |

| 21                      | Domain Specific Processors                                                                                    | 11 |

| 22                      | DRAM & High-Speed Interfaces                                                                                  | 12 |

| 23                      | Analog Techniques II                                                                                          |    |

| 24                      | RF & mm-Wave Power Amplifiers                                                                                 |    |

| 25                      | Digital Power Delivery & Clocking Circuits                                                                    | 15 |

| 26                      | Biomedical Innovations                                                                                        | 6  |

| 27                      | IoT & Security                                                                                                |    |

| 28                      | User Interaction & Diagnostic Technologies                                                                    | 8  |

| 29                      | Emerging RF & THz Techniques4                                                                                 |    |

| 30                      | Efficient Wireless Connectivity                                                                               |    |

| 31                      | Digital Circuit Techniques for Emerging Applications                                                          | 1  |

| 32                      | Power Management Techniques                                                                                   |    |

| 33                      | Non-Volatile Devices for Future Architecture                                                                  |    |

| 34                      | Biomedical Sensing, Stimulation & Harvesting                                                                  | 94 |

|                         | SHORT COURSE                                                                                                  |    |

| SC                      | Circuit Design in Advanced CMOS Technologies —                                                                | 7  |

|                         |                                                                                                               |    |

| F0                      | FORUMS                                                                                                        | 0  |

| F3                      | Machine Learning Processors: From High Performance                                                            | ŏ  |

| F4                      | Applications to Architectures and Benchmarking<br>Cutting Edge Advances in Electrical                         | 0  |

| г4                      | and Optical Transposition Technologies                                                                        | 9  |

| E5                      | and Optical Transceiver Technologies                                                                          | 20 |

| F5<br>F6                | Power Management as an Enabler of Future SoC's                                                                |    |

|                         |                                                                                                               |    |

| Commi                   | ittees                                                                                                        | i9 |

| Conference Information  |                                                                                                               |    |

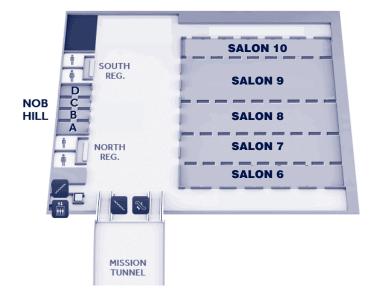

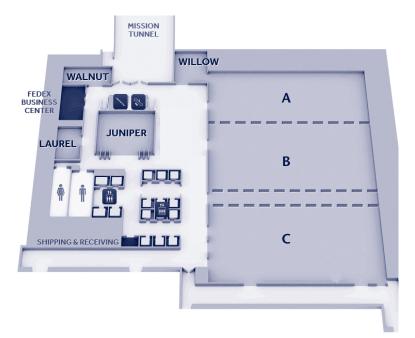

| Conference Space Layout |                                                                                                               |    |

## Sunday February 16th, 8:30 AM

There are a total of 10 tutorials this year on 10 different topics. Each tutorial, selected through a competitive process within each subcommittee of the ISSCC, presents the basic concepts and working principles of a single topic. These tutorials are intended for non-experts, graduate students and practicing engineers who wish to explore and understand a new topic.

### Ali Sheikholeslami

ISSCC Education Chair

#### 8:30 AM

## T1: Fundamentals of Integrated Transformers: From Principles to Applications

Andrea Bevilacqua, University of Padova, Padova, Italy

Integrated magnetic transformers are becoming ubiquitous in mm-wave and RF systems, while also finding application in fully integrated DC-DC converters. This tutorial will cover the fundamentals of transformer operation spanning from the underlying physical principles, to the link between the magnetic parameters (inductances and magnetic coupling) and the inductor geometry, to its use in the design of building blocks like LNAs, PAs, VCOs, etc. The advantages and possibilities of using a transformer for the implementation of baluns, impedance transformation networks, higher-order resonant networks, feedback circuits, etc. will be highlighted.

Andrea Bevilacqua received the Laurea and Ph.D. degrees in Electronics Engineering from the University of Padova, Italy. From 2005 to 2015, he was Assistant Professor with the University of Padova, where he is now Associate Professor. His current research interests include the design of analog and RF/microwave integrated circuits and the analysis of wireless communication systems, radars, and DC-DC converters. He is author or coauthor of more than 90 technical papers, and he holds 5 patents. He serves on the ISSCC and ESSCIRC Technical Program Committees and was TPC Co-Chair of ESSCIRC 2014.

#### 8:30 AM

## T2: Analog Building Blocks of DC-DC Converters

Bernhard Wicht, University of Hannover, Hannover, Germany

System behavior and performance of power management strongly depend on the implementation at the circuit level. This tutorial covers the design of DC-DC converter building blocks such as power switches, gate drivers and their supply, level shifters and error amplifiers, as well as control-loop and current-sensing techniques. Circuits for diagnostics and protection will also be addressed. Increasing switching frequency scales down passive components, but poses a challenge for the design of timing-critical circuits. The tutorial will highlight trade-offs between speed, efficiency, complexity, voltage and current capabilities, etc.

**Bernhard Wicht** has 20+ years of experience in analog and power-management IC design. He received the Dipl. Ing. degree in electrical engineering from TU Dresden, Germany, in 1996 and the Ph.D. degree from TU Munich, Germany, in 2002. Between 2003 and 2010, he was with Texas Instruments, Germany, responsible for the design of automotive ICs for power management, motor control and transceivers. Between 2010 and 2017, he was a full professor and a member of the Robert Bosch Center for Power Electronics at Reutlingen University. Since April 2017, he has been heading the Chair for Mixed-Signal IC Design at Leibniz University Hannover, Germany. 8:30 AM

## T3: Interface Circuits for Wearable and Implantable Sensing Systems

Patrick P. Mercier, University of California, San Diego, La Jolla, CA

Wearable and implantable systems offer an exciting means to monitor human physiology in real time. Such devices require careful interaction between transducers and front-end circuits in order to extract the maximum possible signal-to-noise ratio, while also carefully managing system-level size and power trade-offs. This tutorial will introduce front-end design techniques used in electrophysiological sensing applications, along with emerging trends in physiochemical sensing applications.

**Patrick Mercier** is an Associate Professor of Electrical and Computer Engineering and cofounder/co-director of the Center for Wearable Sensors at UC San Diego. He received his B.Sc. degree from the University of Alberta, and the S.M. and Ph.D. degrees from MIT. His research interests include the design of energy-efficient mixed-signal systems, RF circuits, power converters, and sensor interfaces for wearable, medical, and mobile applications. This has led to over 120 peer-reviewed papers. He has received numerous awards, including the DARPA Young Faculty Award, the NSF CAREER Award, and the 2010 ISSCC Jack Kilby Award. He is an Associate Editor of TBioCAS and SSCL, and is a member of the ISSCC, CICC, and VLSI technical program committees.

#### 10:30 AM

#### T4: Basics of Non-Volatile Memories: MRAM, RRAM, and PRAM Fatih Hamzaoglu, Intel, Hillsboro, OR

NAND Flash and eFlash have been the workhorse of memory hierarchy for standalone storage and embedded non-volatile memories (NVMs), respectively. But with the ever increasing need for memory capacity and bandwidth, due to new applications in graphics, AI and IoT, device and circuit designers have been heavily investigating alternative memories to fill the need. When it comes storage, there is a big gap between DRAM and NAND in terms of density and speed, which could justify a new memory type. When it comes to NVM, growing IoT requires better performance and more power efficient NVM than eFlash, which can be scaled to 1xnm technologies.

This tutorial will talk about the basic characteristics, circuits and system designs for emerging non-volatile memories such as MRAM, RRAM, and PRAM. The tutorial will present the details of MRAM and RRAM, as well as a comparison of these memory devices, and the applications they target.

After finishing the Ph.D. in EE at the University of Virginia in 2002, Fatih joined Logic Tech. Development at Intel. Since then, he has been working on memory developments, such as SRAM, DRAM, MRAM and RRAM. He has served as technical committee member at VLSI Symp. Circuits and ISSCC. He has co-authored more than 40 papers and he's co-inventor of more than 30 patents.

#### 10:30 AM

### T5: Fundamentals of Time-Interleaved ADCs

John P. Keane, Keysight Technologies, Santa Clara, CA

In recent years, time-interleaving analog-to-digital converters (ADCs) have become more popular, especially for high sample rate applications such as wireline communications. This tutorial will cover the fundamentals of time-interleaved sampling, including an introduction to aliasing and an explanation of how mismatch in time-interleaved architectures can cause aliasing artifacts to appear. Practical methods to implement time-interleaved ADCs and combat these mismatch-induced effects will also be presented.

John P. Keane received the Ph.D. degree in Electrical Engineering from the University of California, Davis in 2004. Since then, he has been with Keysight Technologies (formerly Agilent Technologies), Santa Clara, CA, where he is engaged in research on high-performance integrated circuits for measurement applications. His research interests include timing recovery and adaptive equalization for high-speed serial transceivers and the design and calibration of high-resolution data converters. Most recently his focus has been on the design of high-bandwidth time-interleaved analog-to-digital converters. He is a co-author of several IEEE papers and US patents on these topics and is currently a member of the ISSCC technical program committee.

#### 10:30 AM

## T6: Digital Fractional-N Phase-Locked-Loop Design

Mike Shuo-Wei Chen, University of Southern California, Los Angeles, CA

The tutorial overviews the basics of digital fractional-N phase-locked-loop architectures and their design principles from the signal-processing level down to circuit design. We will examine various design constraints and implementation overhead of such architectures due to the inherent digital architecture as well as circuit non-idealities. We will discuss circuit design and calibration techniques. Lastly, some real design examples in silicon with measurement data will be provided.

**Mike Shuo-Wei Chen** is Associate Professor in the Electrical Engineering Department at the University of Southern California (USC) and holds Colleen and Roberto Padovani Early Career Chair position.

He received the B.S. degree from National Taiwan University, Taipei, Taiwan, in 1998 and the M.S. and Ph.D. degree from University of California, Berkeley, in 2002 and 2006, all in Electrical Engineering. As a graduate student researcher, he proposed and demonstrated the asynchronous SAR ADC architecture, which has been adopted today for low-power high-speed analog-to-digital conversion products in industry. At USC, he leads an analog mixed-signal circuit group. He was the recipient of NSF Faculty Early Career Development (CAREER) Award, DARPA Young Faculty Award (YFA) both in 2014.

1:30 PM

## T7: Basics of Digital Low-Dropout (LDO) Integrated Voltage Regulators

Mingoo Seok, Columbia University, New York, NY

Systems-on-chips incorporate integrated low-dropout (LDO) voltage regulators (VRs) to improve energy efficiency by allowing each core on a shared input voltage rail to operate at a unique voltage. LDOs enable compact size, low cost, and relatively simple integration. This tutorial introduces the key trade-offs between analog and digital LDOs and covers the primary specifications. Finally, this tutorial presents a wide range of state-of-the-art digital LDOs while highlighting the key design trade-offs.

**Mingoo Seok** is Associate Professor of Electrical Engineering at Columbia University. He received the B.S. degree with summa cum laude from Seoul National University, South Korea, in 2005, and the M.S. and Ph.D. degrees from the University of Michigan in 2007 and 2011 respectively, all in electrical engineering. His research interest is VLSI hardware, including near-threshold and subthreshold-voltage ultra-low-power hardware, machine-learning hardware, variation-tolerant hardware, on-chip power management, and non-conventional computing such as in-memory computing and hybrid analog-digital computing. He won the 2015 NSF CAREER award. He has been a technical committee member in hardware conferences including the IEEE International Solid-State Circuits Conference (ISSCC).

#### 1:30 PM

## T8: Capacitive Sensor Interfaces

Man-Kay Law, University of Macau, Macau, Macau

Capacitive sensors for displacement, proximity and pressure sensing are widely deployed in various consumer, medical, automotive, and industrial sectors, with the advantages of zero static power consumption and good compatibility with CMOS circuitry. This tutorial provides an overview of the fundamental principles of capacitive sensor interfaces, as well as the design tradeoffs in terms of accuracy and energy consumption. Recent techniques to achieve low-noise and high-efficiency sensing will also be discussed.

**Man-Kay Law** received the B.Sc. degree in Computer Engineering and the Ph.D. degree in Electronic and Computer Engineering from Hong Kong University of Science and Technology. Since 2011, he has been with the State Key Laboratory of Analog and Mixed-Signal VLSI, University of Macau, Macau, China, where he is currently an Associate Professor. His research interests include ultra-low-power sensing circuits and systems, analog and mixed-signal integrated circuits, and energy harvesting techniques. He is a co-recipient of the A-SSCC Distinguished Design Award in 2015, and also the advisor for student awards, including the SSCS Pre-doctoral Achievement Award and the ISSCC Silk-Road Award. He is a member of the Technical Program Committee of ISSCC.

3:30 PM

#### T9: Fundamentals of Wireless Transceiver Circuits and Architectures (from 2G to 5G) Venumadhav Bhagavatula, Samsung Semiconductor, San Jose, CA

Cellular technology has witnessed five generations of evolution - the mobile UE-era ushered in by 2G (GSM/EDGE), to the future smart-phones that will powered by the enhanced spectral efficiency of 5G. Each 'G' improved the user experience while introducing new hardware design challenges. This tutorial follows a top-down approach - we compare 2/3/4/5G system requirements, derive key TX/RX/LO circuit specifications, and highlight the differences in circuit topologies suited for these contrasting specifications. Using this framework, circuit techniques to handle a diverse range of problems such as low phase-noise oscillators, improved blocker tolerance, single-RB linearity, and digital calibration will be introduced.

**Venumadhav Bhagavatula** received the B.E. degree in electronics and communication from the University of Delhi, New Delhi, India, the M.Tech. degree in electronic design technology from the Indian Institute of Science, Bangalore, India, and the Ph.D. degree in electrical engineering from the University of Washington, Seattle, WA, USA, in 2005, 2007, and 2013. Since 2014 he has been with the Advanced Circuit Design group at Samsung Semiconductors Inc., San Jose, CA, USA. His research interests include RF/mm-wave and low-power mixed signal circuits. He currently serves on the technical program committee member for the ISSCC.

#### 3:30 PM

#### T10: How to Understand and Evaluate Deep Learning Processors Vivienne Sze. Massachusets Institute of Technology. Cambridge. MA

There has been a significant amount of specialized hardware being developed for deep learning in both academia and industry. This tutorial aims to highlight the key concepts needed to evaluate and compare deep learning processors. We will discuss existing challenges such as the flexibility and scalability needed to support a wide range of neural networks, as well as design considerations for different platforms. We will also discuss metrics to evaluate and compare existing solutions.

Vivienne Sze is an Associate Professor in the EECS Department at MIT. Her research interests include energy-aware signal processing algorithms, and low-power circuit and system design for applications, such as machine learning, computer vision, autonomous navigation, and video coding. Prior to joining MIT, she was a Member of Technical Staff in the R&D Center at Texas Instruments, where she developed algorithms and hardware for the H.265/HEVC video coding standard, which received the Primetime Engineering Emmy Award. She is a receipient/co-recipient of several awards including the Symposium on VLSI Circuits Best Student Paper Award, the MICRO Top Picks Award, and MIT's Jin-Au Kong Outstanding Doctoral Thesis Prize.

### F1: Millimeter-Wave 5G: From Soup to Nuts and Bolts

- Organizers: Arun Natarajan, Oregon State University, Corvallis, OR

- Committee: Krzysztof Dufrêne, Intel DMCE, Linz, Austria Chan-Hong Chern, TSMC, San Jose, CA Harish Krishnaswamy, Columbia University, New York, NY Jongwoo Lee, Samsung, Hwaseong, Gyeonggi-do, Korea Theodore Georgantas, Broadcom, Greece

Millimeter-wave frequencies have emerged as a promising solution to achieve increased wireless capacity and speed in 5G networks. The forum brings together experts who will describe challenges and state-of-the-art in circuits and architectures for 28GHz/38GHz 5G NR transceivers targeting UE, CPE and infrastructure applications. System-level deployment objectives and real-world constraints will be presented to provide the context for mm-wave transceiver designs. Different device technologies will be considered and system-level requirements will be translated to design approaches for critical building blocks for frequency synthesis, power amplification, RF-PA power supply systems and analog-to-digital conversion. Packaging and test considerations play an integral role in mm-wave transceiver design due to the high operating frequency and large number of elements. Low-cost mm-wave antenna and packaging will be presented along with phased array calibration and test approaches for a holistic overview of future mm-wave 5G landscapes.

|          | Agenda                                                                                                                             |

|----------|------------------------------------------------------------------------------------------------------------------------------------|

| Time     | Торіс                                                                                                                              |

| 8:00 AM  | Breakfast                                                                                                                          |

| 8:10 AM  | Introduction<br>Arun Natarajan, Oregon State University, Corvallis, OR                                                             |

| 8:15 AM  | mm-Wave: From Soup to Nuts Moving it Forward<br>Rob Soni, Nokia Bell Labs, Randolph, NJ                                            |

| 9:00 AM  | 5G mmWave Front-End Technologies and Architectures<br>Bror Peterson, <i>Qorvo, Dallas, TX</i>                                      |

| 9:45 AM  | Transceiver Design for 5G mmWave UE<br>Sang Won Son, Samsung, San Jose, CA                                                         |

| 10:30 AM | Break                                                                                                                              |

| 10:45 AM | Frequency Generation for mm-wave 5G<br>Mike Keaveney, Analog Devices, Limerick, Ireland                                            |

| 11:35 AM | Millimeter-Wave Power Amplifiers for 5G: Status and Prospects<br>Peter Asbeck, UCSD, San Diego, CA                                 |

| 12:25 PM | Lunch                                                                                                                              |

| 1:25 PM  | High Performance ADCs for 5G<br>Benjamin Hershberg, IMEC, Leuven, Belgium                                                          |

| 2:15 PM  | Scalable Approaches of Organic Substrate Implementation<br>for mmWave Antenna in Package<br>Harrison Chang, ASE, Kaohsiung, Taiwan |

| 3:05 PM  | Break                                                                                                                              |

| 3:20 PM  | Beamforming Arrays and their Test and Calibration<br>Brian Floyd, North Carolina State Universty, Raleigh, NC                      |

| 4:10 PM  | Envelope Tracking Modulator for Millimeter-Wave<br>RF Power Amplifiers<br>Chen-Yen Ho, Mediatek, Hsinchu, Taiwan                   |

| 5:00 PM  | Conclusion                                                                                                                         |

|          |                                                                                                                                    |

### F2: ML at the Extreme Edge: Machine Learning as the Killer IoT App

Organizer: Dennis Sylvester, University of Michigan, Ann Arbor, MI

Committee: Meng-Fan (Marvin) Chang, National Tsing Hua University, Hsinchu, Taiwan James Myers, Arm, Cambridge, United Kingdom Naveen Verma, Princeton University, Princeton, NJ

This forum puts a clear focus on machine learning in very low power edge devices (uW to mW), rather than focusing on its use in data centers. While GPUs for training in data centers, and large-scale inference engines are the common case today, the combination of IoT and ML brings new capabilities to edge devices. Speakers will motivate this area and provide insights on the impact of resource constraints on both training and inference in such devices. In addition, key application areas are discussed in depth, namely audio and imaging. The role of new memory-centric design approaches in edge-based ML is also discussed. Finally, the software environment is discussed, to make hardware designers aware of the opportunities for power-constrained ML algorithm implementations.

Agenda

| <u>Time</u> | <u>Topic</u>                                                                                                                                                              |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8:00 AM     | Breakfast                                                                                                                                                                 |

| 8:20 AM     | Introduction<br>Dennis Sylvester, University of Michigan, Ann Arbor, MI                                                                                                   |

| 8:25 AM     | Machine Learning Meets IoT:<br>The Perfect Storm for Innovation in Ultra-Low Power System Design<br>Boris Murmann, Stanford University, Stanford, CA                      |

| 8:50 AM     | TinyML: Ultra-Low Power Edge Al for Autonomous Systems<br>Arijit Raychowdhury, Georgia Institute of Technology, Atlanta, GA                                               |

| 9:40 AM     | Bringing Intelligence to Mobile Platforms:<br>From Deep Learning to Neuromorphic Computing<br>Dongsuk Jeon, Seoul National University, Seoul, Korea                       |

| 10:30 AM    | Break                                                                                                                                                                     |

| 10:45 AM    | Structured Sparsity and Low-Precision Quantization<br>for Energy-/Area-Efficient DNNs<br>Jae-sun Seo, Arizona State University, Tempe, AZ                                 |

| 11:35 AM    | TinyML for Audio-Based Applications<br>Shih-Chii Liu, University of Zurich and ETH Zurich, Switzerland                                                                    |

| 12:25 PM    | Lunch                                                                                                                                                                     |

| 1:25 PM     | Machine Learning for Event-Based Vision:<br>from Low Power Pixels to Low Power Applications<br>Amos Sironi, Prophesee, Paris, France                                      |

| 2:15 PM     | In-Sensor and In-Memory Computing for Constrained Hardware<br>for TinyML IoT Applications<br>Kea-Tiong Tang, National Tsing Hua University, Hsinchu, Taiwan               |

| 3:05 PM     | Break                                                                                                                                                                     |

| 3:20 PM     | Nonvolatile Logic and Smart Nonvolatile Processors<br>with CMOS/MTJ Hybrid Technology for IoT and AI (AloT) Edge System<br>Tetsuo Endoh, Tohoku University, Sendai, Japan |

| 4:10 PM     | How TensorFlow Enables the TinyML Ecosystem<br>Raziel Alvarez, Google, Mountain View, CA                                                                                  |

| 5:00 PM     | Concluding Remarks,<br>Dennis Sylvester, University of Michigan, Ann Arbor, MI                                                                                            |

### EE1: Student Research Preview (SRP)

The Student Research Preview (SRP) will highlight selected student research projects in progress. The SRP consists of approximately 21 ninety-second presentations followed by a Poster Session, by graduate students from around the world, which have been selected on the basis of a short submission concerning their on-going research. Selection is based on the technical quality and innovation of the work. This year, the SRP will be presented in three theme sections: Machine Learning & Digital; Biomedical & Analog; Communications & RF.

The Student Research Preview will include an inspirational lecture by Professor Tadahiro Kuroda. The SRP begins at 7:30 pm on Sunday, February 16th. The SRP is open to all ISSCC registrants.

| Co-Chair:           | Denis Daly           | С |

|---------------------|----------------------|---|

| Co-Chair:           | Jerald Yoo           | Ν |

| Secretary:          | Tinoosh Mohsenin     | U |

| Advisor:            | Anantha Chandrakasan | Ν |

| Advisor:            | Jan Van der Spiegel  | U |

| Media/Publications: | Laura Fujino         | U |

| A/V:                | Trudy Stetzler       | Н |

|                     | inday otominor       |   |

Omni Design Technologies, Billerica, MA National University of Singapore, Singapore University of Maryland, Baltimore, MD MIT, MA University of Pennsylvania, PA University of Toronto, Canada Halliburton, Houston,TX

### **COMMITTEE MEMBERS**

Jason Anderson University of Toronto, Canada Masoud Babaie Delft University of Technology, The Netherlands Andrea Baschirotto University of Milan-Bicocca. Italy Hsin-Shu Chen National Taiwan University, Taiwan Hayun Chung Korea University, Korea Denis Dalv Omni Design Technologies, MA Shidhartha Das Arm. United Kinadom Zeynep Deniz IBM, NY Hao Gao Eindhoven University of Technology, The Netherlands Minkvu Je KAIST. Korea Matthias Kuhl Hamburg University of Technology, Germany Seulki Lee imec-Netherlands, The Netherlands Yoonmyung Lee SungKyunKwan University, Korea Qiang Li University of Electronic Science & Technology, China Shih-Chii Liu University of Zurich/ETH Zurich, Switzerland Carolina Mora Lopez IMEC. Belaium Shahriar Mirabbasi University of British Columbia, Canada University of Maryland, MD Tinoosh Mohsenin Cormac O'Connell TSMC. Kanata. Canada Intel, MA Mondira Pant Negar Reiskarimian MIT, MA Arizona State University, AZ Jae-sun Seo Atsushi Shirane Tokyo Institute of Technology, Japan Yildiz Sinangil Apple, CA GuoXing Wang Shanghai Jiao Tong University, China Jeffrey Weldon University of Hawaii, HI Chia-Hsiang Yang National Taiwan University, Taiwan Rabia Tugce Yazicigil Boston University, MA Jerald Yoo National University of Singapore, Singapore Samira Zaliasl Ferric, NY Tsinghua University, Beijing, China Milin Zhang

### EE2: Rising Stars 2020 Workshop

| Chair:    | Farhana Sheikh, Intel, Hillsboro, OR           |  |  |

|-----------|------------------------------------------------|--|--|

| Co-Chair: | Rabia Yazicigil, Boston University, Boston, MA |  |  |

#### Rising Stars 2020 Workshop Committee:

Zeynep Deniz, IBM Dina R. El-Damak, University of Southern California Q. Jane Gu, University of California, Davis Ulkuhan Guler, Worcester Polytechnic Institute Alicia Klinefelter, NVIDIA Rikky Muller, University of California, Berkeley Negar Reiskarimian, MIT Yildiz Sinangil, Apple Trudy Stetzler, Halliburton Alice Wang, Everactive Kathy Wilcox, AMD

#### Advisory Board:

Tsu-Jae K. Liu, U. C. Berkeley Andrea Goldsmith, Stanford University Anantha Chandrakasan, MIT

The IEEE SSCS Women in Circuits together with ISSCC will be sponsoring the first "Rising Stars 2020" for young professionals and students. The Rising Stars 2020 is an educational workshop for graduate and undergraduate students, and young professionals who have graduated within the last two years who are interested in learning how to excel at academic and industry careers in computer science, computer and electrical engineering. "*Rising to the Top in Industry*" career panel will touch upon topics such as mentoring, setting career goals, filing patents, management vs. technical tracks, and more. "*Navigating the Assistant Professorship*" will address applying for a faculty position, tenure review, and managing day-to-day life in academia. The panels are open to the all ISSCC 2020 attendees and the public. In addition to the panels, we will be selecting 20 rising stars in academia and industry to attend a special dinner, keynote from a high-profile already "Risen Star", and mentoring session.

| Time           | Rising Stars 2020                                           |

|----------------|-------------------------------------------------------------|

| 4:00 – 5:00 PM | Welcome, Introductions, Posters, Networking, and Photos     |

| 5:00 – 6:30 PM | Dinner, Keynote, and Mentoring                              |

| 6:30 - 7:30 PM | Navigating the Assistant Professorship (Open to the public) |

| 6:30 - 7:30 PM | Rising to the Top in Industry (Open to the Public)          |

#### 4:00PM – 5:00PM Welcome, Posters, and Networking

4:00PM – 5:10PM Workshop Opening and Introduction Farhana Sheikh, Intel and Rabia Yazicigil, Boston University

> 4:10PM – 4:30PM Poster Introductions Presented by Rising Stars

> > 4:30PM – 5:00PM Networking

**EVENING EVENT**

Sunday February 16th, 5:00 PM

### **Rising Stars 2020 Dinner, Keynote, and Mentoring**

#### 5:00PM – 5:30PM

Introductions and Dinner

Farhana Sheikh, Intel and Kathy Wilcox, AMD

5:30PM - 6:00PM

Rising Stars 2020 Workshop Dinner Keynote (closed to selected Rising Stars) Speaker: Anantha Chandrakasan, MIT

6:00PM - 6:30PM

Rising Stars 2020 Workshop Mentoring Session (closed to selected Rising Stars)

#### 6:30PM - 7:30PM

Navigating the Assistant Professorship - Academia Career Panel (open to the public)

#### Distinguished Panel Speaker:

"Words of Wisdom", Azita Emami, California Institute of Technology

The panel will provide perspectives from professors and rising stars in the academic field on the faculty application process, the necessary steps to increase your chances of being hired, and the requirements at the tenure review. The panel will provide participants with practical information and candid advice on seeking and interviewing for faculty jobs, networking, teaching, speaking, mentoring, funding research, setting up labs, getting tenure, and managing day-to-day life in academia.

Panel Moderators: Dina Reda El-Damak, University of Southern California Q. Jane Gu, University of California, Davis

Panelists:

Vivienne Sze, MIT Esther Rodriguez Villegas, Imperial College, London, UK Jerald Yoo, National University of Singapore Zhengya Zhang, University of Michigan Milin Zhang, Tsinghua University

#### 6:30PM - 7:30PM

Rising to the Top in Industry - Industry Career Panel (Open to the Public)

#### **Distinguished Panel Speaker**

"Words of Wisdom", Alice Wang, VP, Everactive

The industry career panel will tackle the question of how to become a rising star in the corporate world. Our diverse panelists bring their own experiences and perspectives from small startup organizations to large corporations, including corporate research labs. The panel will touch upon topics such as mentoring, setting career goals, deciding between management and technical tracks, publishing and filing patents, collaborating across diverse teams, and working effectively in a team. The goal is to provide the audience with the know-how to successfully navigate challenges in the corporate world, and rise to the top.

| Panel Moderators: | Alicia Klinefelter, NVIDIA<br>Zeynep Deniz, IBM                                                              |

|-------------------|--------------------------------------------------------------------------------------------------------------|

| Panelists:        | Wendy Belluomini, IBM<br>Mike Mulligan, Silicon Labs<br>Kazuko Nishimura, Panasonic<br>Walker Turner, NVIDIA |

|                   | Walker Turner, NVIDIA                                                                                        |

Laura Fick, Mythic Al

## Plenary Session — Invited Papers

**Chair:** Jan van der Spiegel, University of Pennsylvania, Philadelphia, PA ISSCC Conference Chair

Associate Chair: Un-Ku Moon, Oregon State University, Corvallis, OR ISSCC International Technical Program Chair

#### FORMAL OPENING OF THE CONFERENCE 8:30 AM

#### 1.1 The Deep Learning Revolution and Its Implications 8:45 AM for Computer Architecture and Chip Design

Jeff Dean, Google, Mountain View, CA

The past decade has seen a remarkable series of advances in machine learning, and in particular deep learning approaches based on artificial neural networks, to improve our abilities to build more accurate systems across a broad range of areas, including computer vision, speech recognition, language translation, and natural language understanding tasks. In this talk, I will highlight some of these advances, and their implications on the kinds of computational devices we need to build, especially in an era where general purpose computers are no longer improving their performance significantly year-over-year. I'll also discuss some of the ways that machine learning may also be able to help with some aspects of the circuit design process. Finally, I'll provide a sketch of at least one interesting direction towards much larger-scale multi-task models that are sparsely activated and employ much more dynamic, example- and task-based routing than the machine learning models of today.

#### 1.2 Fertilizing AloT from Roots to Leaves

9:20 AM

#### Kou-Hung Lawrence Loh, MediaTek, Hsinchu, Taiwan

Artificial intelligence (AI) creates new opportunities for all kinds of "things" to interface with the universe in unprecedented ways. As IC technology advances, AI has evolved from traditional expert systems toward cognitive intelligence, which involves multidimensional perception, self-learning, decision-making, and interaction. Enabling cognitive AI in everything (AloT) demands comprehensive circuit technologies to enhance the performance, power dissipation, and form factor of edge devices as well as cloud infrastructure, which forms the roots to support a variety of leaf-applications. The root-technologies are far ranging, including Al Processing Unit (APU), multi-processor computing, 5G, high-speed wireline communication between edge and the cloud, emerging storage technology, human-machine interfaces, and advanced SoC packages. These fundamental technologies enable intelligent applications spanning across mobile devices, smart home, automotive platform, and smart city. This talk will discuss the advancement of these root technologies that are driving the current transition from conventional ICs to AloT. Through the discussion, technical innovations for Edge AI SoC and Cloud-Edge collaboration enabled by emerging wireless and wireline communication standards will be explored. To reach the vision of over 350 billion connected intelligent devices in 2030, the challenges and opportunities for our industry going forward will be summarized.

| ISSCC, SSCS, IEEE AWARD PRESENTATIONS | 9:55 AM  |

|---------------------------------------|----------|

| BREAK                                 | 10:20 AM |

#### 1.3 Future Scaling: Where Systems and Technology Meet 10:40 AM

#### Nadine Collaert, imec, Leuven, Belgium

In a smart society where everything will be connected, an avalanche of data is coming toward us, with numbers going to several hundreds of zettabytes per year by 2025. This data will need to be sent around, stored, computed and analyzed. At the heart of it all will be innovations at the technology and system level. With Moore's law under pressure, a rethinking of what the semiconductor industry calls scaling will be needed.

In this work, we will show the strong push to technology diversification, blending different technologies together to achieve benefits at the system level. This brings the interaction of technology and design to the next level: System-Technology co-optimization (STCO), with 3D technologies taking a central stage. Furthermore, the growing demand for storage will put an increasing pressure on the memory hierarchy where emerging concepts like MRAM, FeFET.... have the potential to bring new speed and capacity benefits. Next to that, memories like e.g. RRAM are getting a lot of traction for analog in-memory computing to enable energy efficient machine learning at the IoT edge. Finally, we will also briefly review the status of quantum computing, these days gaining a lot of interest as a path to ultra-powerful computing.

#### 1.4 The Future of Computing: Bits + Neurons + Qubits 11:15 AM

Dario Gil, IBM Thomas J. Watson Research Center, Yorktown Heights, NY

The laptops, cell phones, and internet applications commonplace in our daily lives are all rooted in the idea of zeros and ones – in bits.

This foundational element originated from the combination of mathematics and Claude Shannon's Theory of Information. Coupled with the 50-year legacy of Moore's law, the bit has propelled the digitization of our world.

In recent years, artificial intelligence systems, merging neuron-inspired biology with information, have achieved superhuman accuracy in a range of narrow classification tasks by learning from labelled data. Advancing from narrow AI to broad AI will encompass the unification of learning and reasoning through neuro-symbolic systems, resulting in a form of AI which will perform multiple tasks, operate across multiple domains, and learn from small quantities of multi-modal input data.

Finally, the union of physics and information led to the emergence of Quantum Information Theory and the development of the quantum bit - the qubit - forming the basis of quantum computers. We have built the first programmable quantum computers, and although the technology is still in its early days, these systems offer the potential to solve problems which even the most powerful classical computers cannot.

The future of computing will look fundamentally different that it has in the past. It will not be based on more and cheaper bits alone, but rather, it will be built upon bits + neurons + qubits. This future will enable the next generation of intelligent mission critical systems and accelerate the rate of science-driven discovery.

#### PRESENTATION TO PLENARY SPEAKERS

11:50 AM

11:55 AM

#### CONCLUSION

### Processors

Session Chair: Christopher Gonzalez, IBM, Yorktown Heights, NY Session Co-Chair: Thomas Burd, Advanced Micro Devices, Santa Clara, CA

1:30 PM

## 2.1 Zen 2: The AMD 7nm Energy-Efficient High-Performance x86-64

T. Singh<sup>1</sup>, S. Rangarajan<sup>1</sup>, D. John<sup>1</sup>, R. Schreiber<sup>1</sup>, S. Oliver<sup>1</sup>, R. Seahra<sup>2</sup>, A. Schaefer<sup>1</sup> <sup>1</sup>AMD, Austin, TX; <sup>2</sup>AMD, Markham, ON, Canada

2:00 PM

#### 2.2 AMD Chiplet Architecture for High-Performance Server and Desktop Products

*S. Naffziger*<sup>1</sup>, *K. Lepak*<sup>2</sup>, *M. Paraschou*<sup>1</sup>, *M. Subramony*<sup>2</sup> <sup>1</sup>AMD, Fort Collins, CO; <sup>2</sup>AMD, Austin, TX

2:30 PM

#### 2.3 A 220GOPS 96-Core Processor with 6 Chiplets 3D-Stacked on an Active Interposer Offering 0.6ns/mm Latency, 3Tb/s/mm<sup>2</sup> Inter-Chiplet Interconnects and 156mW/mm<sup>2</sup> @ 82%-Peak-Efficiency DC-DC Converters

P. Vivet<sup>1</sup>, E. Guthmuller<sup>1</sup>, Y. Thonnart<sup>1</sup>, G. Pillonnet<sup>1</sup>, G. Moritz<sup>1</sup>, I. Miro-Panadès<sup>1</sup>, C. Fuguet<sup>1</sup>, J. Durupt<sup>1</sup>, C. Bernard<sup>1</sup>, D. Varreau<sup>1</sup>, J. Pontes<sup>1</sup>, S. Thuries<sup>1</sup>, D. Coriat<sup>1</sup>, M. Harrand<sup>1</sup>, D. Dutoit<sup>1</sup>, D. Lattard<sup>1</sup>, L. Arnaud<sup>1</sup>, J. Charbonnier<sup>1</sup>, P. Coudrain<sup>1</sup>, A. Garnier<sup>1</sup>, F. Berger<sup>1</sup>, A. Gueugnot<sup>1</sup>, A. Greiner<sup>2</sup>, O. Meunier<sup>2</sup>, A. Farcy<sup>3</sup>, A. Arriordaz<sup>4</sup>, S. Cheramy<sup>1</sup>, F. Clermidy<sup>1</sup> ICEA-LETI-MINATEC, Grenoble, France; <sup>2</sup>Sorbonne University, Paris, France <sup>3</sup>STMicroelectronics, Crolles, France; <sup>4</sup>Mentor, St. Ismier, France

Break 3:00 PM

#### 3:15 PM

#### 2.4 A 7nm High-Performance and Energy-Efficient Mobile Application Processor with Tri-Cluster CPUs and a Sparsity-Aware NPU

Y. D. Kim, W. Jeong, L. Jung, D. Shin, J. G. Song, J. Song, H. Kwon, J. Lee, J. Jung, M. Kang, J. Jeong, Y. Kwon, N. H. Seong, Samsung Electronics, Hwaseong, Korea

#### 3:45 PM

#### 2.5 A 7nm FinFET 2.5GHz/2.0GHz Dual-Gear Octa-Core CPU Subsystem with Power/Performance Enhancements for a Fully Integrated 5G Smartphone SoC

H. Mair<sup>1</sup>, E. Wang<sup>2</sup>, A. Nayak<sup>1</sup>, R. Lagerquist<sup>1</sup>, L. Chou<sup>2</sup>, G. Gammie<sup>1</sup>, H. Chen<sup>1</sup>, L-K. Yong<sup>1</sup>, M. Rahman<sup>1</sup>, J. Wiedemeier<sup>1</sup>, R. Madhavaram<sup>1</sup>, A. Chiou<sup>2</sup>, B. Li<sup>2</sup>, V. Lin<sup>2</sup>, R. Huang<sup>2</sup>, M. Yang<sup>2</sup>, A. Thippana<sup>1</sup>, O. Su<sup>2</sup>, S. Huang<sup>2</sup>, <sup>1</sup>MediaTek, Austin, TX; <sup>2</sup>MediaTek, Hsinchu, Taiwan

4:15 PM

#### 2.6 A 16nm 3.5B Transistor >14TOPS 2-to-10W Multicore SoC Platform for Automotive and Embedded Applications with Integrated Safety MCU, 512b Vector VLIW DSP, Embedded Vision and Imaging Acceleration

R. Venkatasubramanian<sup>1</sup>, D. Steiss<sup>1</sup>, G. Shurtz<sup>2</sup>, T. Anderson<sup>1</sup>, K. Chirca<sup>1</sup>, R. Santhanagopal<sup>1</sup>, N. Nandan<sup>1</sup>, A. Reghunath<sup>1</sup>, H. Sanghvi<sup>1</sup>, D. Wu<sup>1</sup>, A. Chachad<sup>1</sup>, B. Karguth<sup>1</sup>, D. Beaudoin<sup>1</sup>, C. Fuoco<sup>1</sup>, L. Nardini<sup>1</sup>, C. Hu<sup>1</sup>, S. Visalli<sup>1</sup>, A. Mundra<sup>1</sup>, D. Varadarajan<sup>1</sup>, F. Cano<sup>2</sup>, S. Stelmach<sup>1</sup>, M. Mody<sup>3</sup>, A. Redfern<sup>1</sup>, H. Bilhan<sup>1</sup>, M. Sarraj<sup>1</sup>, A. Siddiki<sup>1</sup>, A. Lell<sup>1</sup>, E. Falik<sup>1</sup>, A. Hill<sup>1</sup>, A. Armstrong<sup>1</sup>, T. Beck<sup>1</sup>, V. Kanumuri<sup>1</sup>, S. Mullinnix<sup>1</sup>, D. Moore<sup>1</sup>, J. Jones<sup>2</sup>, M. Koul<sup>1</sup>, S. Agarwala<sup>1</sup> <sup>1</sup>Texas Instruments, Dallas, TX; <sup>2</sup>Texas Instruments, Houston, TX <sup>3</sup>Texas Instruments, Bangalore, India

#### 4:45 PM

#### 2.7 IBM z15: A 12-Core 5.2GHz Microprocessor

C. Berry<sup>1</sup>, B. Bell<sup>p</sup>, A. Jatkowski<sup>1</sup>, J. Surprise<sup>1</sup>, J. Isakson<sup>3</sup>, O. Geva<sup>1</sup>, B. Deskin<sup>4</sup>, M. Cichanowski<sup>3</sup>, D. Hamid<sup>1</sup>, C. Cavitt<sup>1</sup>, G. Fredeman<sup>1</sup>, A. Saporito<sup>1</sup>, A. Mishra<sup>5</sup>, A. Buyuktosunoglu<sup>6</sup>, T. Webel<sup>7</sup>, P. Lobo<sup>5</sup>, P. Parashurama<sup>5</sup>, R. Bertran<sup>8</sup>, D. Chidambarrao<sup>9</sup>, D. Wolpert<sup>1</sup>, B. Bruen<sup>1</sup>

<sup>1</sup>IBM Systems and Technology, Poughkeepsie, NY; <sup>2</sup>IBM Systems and Technology, Rochester, NY <sup>3</sup>IBM Systems and Technology, Austin, TX; <sup>4</sup>IBM Systems and Technology, Endicott, NY

<sup>5</sup>IBM Systems and Technology, Bangalore, India

<sup>6</sup>IBM T. J. Watson Reseach Center, Yorktown Heights, NY

<sup>7</sup>IBM Systems and Technology, Boeblingen, Germany

<sup>8</sup>IBM Systems and Technology, Yorktown Heights, NY

<sup>9</sup>IBM Systems and Technology, Hopewell Junction, NY

## **Analog Techniques I**

Session Chair: Youngcheol Chae, Yonsei University, Seoul, Korea Session Co-Chair: Michael Perrott, Texas Instruments, Manchester, NH

1:30 PM

#### 3.1 An Integrated BAW Oscillator with <±30ppm Frequency Stability Over DS1 Temperature, Package Stress, and Aging Suitable for High-Volume Production

D. Griffith<sup>1</sup>, E. T-T. Yen<sup>2</sup>, K. Tsai<sup>1</sup>, H. U. R. Mohammed<sup>1</sup>, B. Haroun<sup>1</sup>, A. Kiae<sup>2</sup>, A. Bahai<sup>2</sup> <sup>1</sup>Texas Instruments, Dallas, TX; <sup>2</sup>Texas Instruments, Santa Clara, CA

#### 2:00 PM

#### 3.2 A 0.0088mm<sup>2</sup> Resistor-Based Temperature Sensor Achieving 92fJ·K<sup>2</sup> FoM in 65nm CMOS

A. Khashaba, J. Zhu, A. Elmallah, M. Ahmed, P. Hanumolu University of Illinois, Urbana, IL

#### 2:30 PM

## 3.3 A 0.51nW 32kHz Crystal Oscillator Achieving 2ppb Allan Deviation Floor DS1 Using High-Energy-to-Noise-Ratio Pulse Injection

L. Xu<sup>1</sup>, T. Jang<sup>2</sup>, J. Lim<sup>1</sup>, K. Choo<sup>1</sup>, D. Blaauw<sup>1</sup>, D. Sylvester<sup>1</sup> <sup>1</sup>University of Michigan, Ann Arbor, MI; <sup>2</sup>ETH Zürich, Zürich, Switzerland

Break 3:00 PM

#### 3:15 PM

### 3.4 A 16MHz CMOS RC Frequency Reference with ±400ppm Inaccuracy from -45°C to 85°C after Digital Linear Temperature Compensation

*Ç. Gürleyük, S. Pan, K.A.A. Makinwa* Delft University of Technology, Delft, The Netherlands

3:45 PM

#### 3.5 A 34µW 32MHz RC Oscillator with ±530ppm Inaccuracy from -40°C to 85°C and 80ppm/V Supply Sensitivity Enabled by Pulse-Density Modulated Resistors

A. Khashaba, J. Zhu, M. Ahmed, N. Pal, P. K. Hanumolu University of Illinois, Urbana, IL

4:15 PM

## 3.6 A CMOS Resistor-Based Temperature Sensor with a 10fJ-K<sup>2</sup> Resolution FoM and 0.4°C ( $3\sigma$ ) Inaccuracy From -55°C to 125°C After a 1-point Trim

S. Pan, K.A.A. Makinwa, Delft University of Technology, Delft, The Netherlands

#### 4:45 PM

#### 3.7 A 620µW BJT-Based Temperature-to-Digital Converter with 0.65mK Resolution and FoM of 190fJ·K<sup>2</sup>

S. Heidary Shalmany<sup>1</sup>, K. Souri<sup>1</sup>, U. Sonmez<sup>1</sup>, K. Souri<sup>2</sup>, M. D'Urbino<sup>1</sup>, S. Hussaini<sup>1</sup>, D. Tauro<sup>2</sup>, S. Tabatabaei<sup>2</sup>

<sup>1</sup>SiTime, Delft, The Netherlands; <sup>2</sup>SiTime, Santa Clara, CA

#### 5:00 PM

#### 3.8 A 23.6ppm/°C Monolithically Integrated GaN Reference Voltage Design with Temperature Range from -50°C to 200°C and Supply Voltage Range from 3.9 to 24V

*C-H. Liao*<sup>1</sup>, *S-H. Yang*<sup>1</sup>, *M-Y. Liao*<sup>1</sup>, *K-C. Chung*<sup>1</sup>, *N. Kumari*<sup>1</sup>, *K-H. Chen*<sup>1</sup>, *Y-H. Lin*<sup>2</sup>, *S-R. Lin*<sup>3</sup>, *T-Y. Tsa*<sup>2</sup>, *Y-Z. Juang*<sup>4</sup> <sup>1</sup>National Chiao Tung University, Hsinchu, Taiwan <sup>2</sup>Realtek Semiconductor, Hsinchu, Taiwan <sup>3</sup>Realtek Semiconductor, Hsinchu City, Taiwan <sup>4</sup>Taiwan Semiconductor Research Institute (TSRI), Hsinchu, Taiwan

## mm-Wave Wireless for Communication & Radar

Session Chair: Matteo Bassi, Infineon Technologies Austria AG, Villach, Austria Session Co-Chair: Vito Giannini, Uhnder, Austin, TX

1:30 PM

#### 4.1 A 39GHz-Band CMOS 16-Channel Phased-Array Transceiver IC with a Companion Dual-Stream IF Transceiver IC for 5G NR Base-Station Applications

H-C. Park, D. Kang, S. M. Lee, B. Park, K. Kim, J. Lee, Y. Aoki, Y. Yoon, S. Lee, D. Lee, D. Kwon, S. Kim, J. Kim, W. Lee, C. Kim, S. Park, J. Park, B. Suh, J. Jang, M. Kim, D. Minn, I. Park, S. Kim, K. Min, J. Park, S. Jeon, A-S. Ryu, Y. Cho, S. T. Choi, K. H. An, Y. Kim, J. H. Lee, J. Son, S-G. Yang, Samsung Electronics, Suwon, Korea

2:00 PM

# 4.2 An E-Band High-Linearity Antenna-LNA Front-End with 4.8dB NF and 2.2dBm IIP3 Exploiting Multi-Feed On-Antenna Noise-Canceling and G<sub>m</sub>-Boosting

*S. Li<sup>1</sup>, T. Chi<sup>2</sup>, D. Jung<sup>1</sup>, T-Y. Huang<sup>1</sup>, M-Y. Huang<sup>1</sup>, H. Wang<sup>1</sup>* <sup>1</sup>Georgia Institute of Technology, Atlanta, GA; <sup>2</sup>Rice University, Houston, TX

2:30 PM

#### 4.3 A 28GHz 4-Element MIMO Beam-Space Array in 65nm CMOS with Simultaneous Spatial Filtering and Single-Wire Frequency-Domain Multiplexing

R. Garg<sup>1</sup>, G. Sharma<sup>\*1</sup>, A. Binaie<sup>\*2</sup>, S. Jain<sup>\*1</sup>, S. Ahasan<sup>\*2</sup>, A. Dascurcu<sup>2</sup>, H. Krishnaswamy<sup>2</sup>, A. Natarajan<sup>1</sup> \*Equally-Credited Authors (ECAs), <sup>1</sup>Oregon State University, Corvallis, OR

\*Equally-Credited Authors (ECAs), 10regon State University, Corvallis, OR 2Columbia University, New York, NY

2:45 PM

#### 4.4 A 28/37GHz Scalable, Reconfigurable Multi-Layer Hybrid/Digital MIMO Transceiver for TDD/FDD and Full-Duplex Communication

S. Mondal, L. R. Carley, J. Paramesh, Carnegie Mellon University, Pittsburgh, PA

Break 3:00 PM

3:15 PM

## 4.5 A 64Gb/s 1.4pJ/b/element 60GHz 2×2-Element Phased-Array Receiver with 8b/symbol Polarization MIMO and Spatial Interference Tolerance

A. Chakrabarti, C. Thakkar, S. Yamada, D. Choudhury, J. Jaussi, B. Casper Intel, Hillsboro, OR

3:45 PM

#### 4.6 Space-Time Modulated 71-to-76GHz mm-Wave Transmitter Array for Physically Secure Directional Wireless Links

X. Lu<sup>\*1</sup>, S. Venkatesh<sup>\*1</sup>, B. Tang<sup>2</sup>, K. Sengupta<sup>1</sup>, \*Equally-Credited Authors (ECAs) <sup>1</sup>Princeton University, Princeton, NJ; <sup>2</sup>Xi'an Jiaotong University, Xi'an, China

4:15 PM

## 4.7 A Single-Antenna W-Band FMCW Radar Front-End Utilizing Adaptive **DS1** Leakage Cancellation

*M. Kalantari<sup>1,2</sup>, H. Shirinabadi<sup>3</sup>, A. Fotowat-Ahmadi<sup>2</sup>, C. P. Yue<sup>1</sup>* <sup>1</sup>Hong Kong University of Science and Technology, Hong Kong, China <sup>2</sup>Sharif University of Technology, Tehran, Iran; <sup>3</sup>University of California, Berkeley, CA

4:45 PM

#### 4.8 A Terahertz FMCW Comb Radar in 65nm CMOS with 100GHz Bandwidth

DS1 X. Yi<sup>1</sup>, C. Wang<sup>1</sup>, M. Lu<sup>1</sup>, J. Wang<sup>1</sup>, J. Grajal<sup>1,2</sup>, R. Han<sup>1</sup> <sup>1</sup>Massachusetts Institute of Technology, Cambridge, MA <sup>2</sup>Universidad Politécnica de Madrid, Madrid, Spain

#### Imagers and ToF Sensors

Session Chair: Seong-Jin Kim, Ulsan National Institute of Science and Technology, Ulsan, Korea Session Co-Chair: Havato Wakabavashi, Sonv Semiconductor Solutions, Atsuai, Japan

1:30 PM

#### 5.1 A 240×192Pixel 10fps 70klux 225m-Range Automotive LiDAR SoC Using DSA a 40ch 0.0036mm<sup>2</sup> Voltage/Time Dual-Data-Converter-Based AFE

S. Kondo', H. Kubota², H. Katagʻri², Y. Ota², M. Hirono³, T. T. Ta', H. Okuni', S. Ohtsuka², Y. Ojima², T. Sugimoto², H. Ishii², K. Yoshioka', K. Kimura², A. Sai', N. Matsumoto², 'Toshiba, Kawasaki, Japan <sup>2</sup>Toshiba Electronic Devices & Storage, Kawasaki, Japan; <sup>3</sup>Toshiba, Yokohama, Japan

2:00 PM

A 1200×900 6µm 450fps Geiger-Mode Vertical Avalanche Photodiodes CMOS Image 5.2 DS1 Sensor for a 250m Time-of-Flight Ranging System Using Direct-Indirect-Mixed Frame Synthesis with Configurable-Depth-Resolution Down to 10cm

T. Okino, S. Yamada, Y. Sakata, S. Kasuga, M. Takemoto, Y. Nose, H. Koshida, M. Tamaru, Y. Sugiura, S. Saito, S. Koyama, M. Mori, Y. Hirose, M. Sawada, A. Odagawa, T. Tanaka Panasonic, Nagaokakyo, Japan

2:15 PM

#### 5.3 An Up-to-1400nm 500MHz Demodulated Time-of-Flight Image Sensor on a DS1 Ge-on-Si Platform

C-L. Chen\*, S-W. Chu\*, B-J. Chen\*, Y-F. Lyu\*, K-C. Hsu\*, C-F. Liang\*, S-S. Su, M-J. Yang, C-Y. Chen, S-L. Cheng, H-D. Liu, C-T. Lin, K. P. Petrov, H-W. Chen, K-C. Chu, P-C. Wu, P-T. Huang, N. Na, S-L. Chen, \*Equally-Credited Authors (ECAs), Artilux, Hsinchu, Taiwan

2:30 PM

5.4 A Dynamic Pseudo 4-Tap CMOS Time-of-Flight Image Sensor with Motion DS1 Artifact Suppression and Background Light Cancelling Over 120klux

D. Kim<sup>1</sup>, S. Lee<sup>2</sup>, D. Park<sup>2</sup>, C. Piao<sup>1</sup>, J. Park<sup>1</sup>, Y. Ahn<sup>1</sup>, K. Cho<sup>1</sup>, J. Shin<sup>3</sup>, S. M. Song<sup>3</sup>, S-J. Kim<sup>2</sup>, J-H. Chun<sup>1</sup>, J. Choi<sup>1</sup>, <sup>1</sup>Sungkyunkwan University, Suwon, Korea

<sup>2</sup>Ulsan National Institute of Science and Technology, Ulsan, Korea; <sup>3</sup>Zeeann, Hanam, Korea Break 3:00 PM

3:15 PM

5.5 A 2.1e Temporal Noise and -105dB Parasitic Light Sensitivity Backside-Illuminated 2.3µm-Pixel Voltage-Domain Global Shutter CMOS Image Sensor Using High-**Capacity DRAM Capacitor Technology**

J-K. Lee, S. S. Kim, I-G. Baek, H. Shim, T. Kim, T. Kim, J. Kyoung, D. Im, J. Choi, K. Cho, D. Kim, H. Lim, M-W. Seo, J. Kim, D. Kwon, J. Song, J. Kim, M. Jang, J. Moon, H. Kim, C. K. Chang, J. Kim, K. Koh, H. Lim, J. Ahn, H. Hong, K. Lee, H-K. Kang, Samsung Electronics, Hwaseong, Korea 3:30 PM

#### 5.6 A 1/2.65in 44Mpixel CMOS Image Sensor with 0.7µm Pixels Fabricated in

Advanced Full-Depth Deep-Trench Isolation Technology H. Kim, J. Park, I. Joe, D. Kwon, J. H. Kim, D. Cho, T. Lee, C. Lee, H. Park, S. Hong, C. Chang, J. Kim, H. Lim, Y. Oh, Y. Kim, S. Nah, S. Jung, J. Lee, J. Ahn, H. Hong, K. Lee, H-K. Kang Samsung Electronics, Hwaseong, Korea

3:45 PM

#### 5.7 A 132dB Single-Exposure-Dynamic-Range CMOS Image Sensor with High Temperature Tolerance

Y. Sakano<sup>1</sup>, T. Toyoshima<sup>1</sup>, R. Nakamura<sup>1</sup>, T. Asatsuma<sup>1</sup>, Y. Hattori<sup>1</sup>, T. Yamanaka<sup>2</sup>, R. Yoshikawa<sup>2</sup>, N. Kawazu<sup>1</sup>, T. Matsuura<sup>1</sup>, T. Iinuma<sup>1</sup>, T. Toya<sup>1</sup>, T. Watanabe<sup>2</sup>, A. Suzuki<sup>1</sup>, Y. Motohashi<sup>1</sup>, J. Azami<sup>1</sup>, Y. Tateshita<sup>1</sup>, T. Haruta<sup>1</sup>, <sup>1</sup>Sony Semiconductor Solutions, Atsugi, Japan <sup>2</sup>Sony Semiconductor Manufacturing, Kikuyo, Japan

4:15 PM

#### A 0.50e<sub>rms</sub> Noise 1.45µm-Pitch CMOS Image Sensor with Reference-Shared 5.8 In-Pixel Differential Amplifier at 8.3Mpixel 35fps

M. Sato, Y. Yorikado, Y. Matsumura, H. Naganuma, E. Kato, T. Toyofuku, A. Kato, Y. Oike Sony Semiconductor Solutions, Atsugi, Japan

4:30 PM

#### 5.9 A 0.8V Multimode Vision Sensor for Motion and Saliency Detection with Ping-Pong PWM Pixel

T-H. Hsu", Y-K. Chen\*, J-S. Wu, W-C. Ting, C-T. Wang, C-F. Yeh, S-H. Sie, Y-R. Chen, R-S. Liu, C-C. Lo, K-T. Tang, M-F. Chang, C-C. Hsieh, \*Equally-Credited Authors (ECAs) National Tsing Hua University, Hsinchu, Taiwan

4:45 PM

#### A 1280×720 Back-Illuminated Stacked Temporal Contrast Event-Based Vision 5.10 DS1 Sensor with 4.86µm Pixels, 1.066GEPS Readout, Programmable Event-Rate **Controller and Compressive Data-Formatting Pipeline**

T. Finateu<sup>1</sup>, A. Niwa<sup>2</sup>, D. Matolin<sup>1</sup>, K. Tsuchimoto<sup>2</sup>, A. Mascheroni<sup>1</sup>, E. Reynaud<sup>1</sup>, P. Mostafalu<sup>3</sup>, F. Brady<sup>3</sup>, L. Chotard<sup>1</sup>, F. LeGoff<sup>1</sup>, H. Takahashi<sup>2</sup>, H. Wakabayashi<sup>2</sup>, Y. Oike<sup>2</sup>, C. Posch<sup>1</sup> <sup>1</sup>PROPHESEE, Paris, France <sup>2</sup>Sony Semiconductor Solutions, Atsugi, Japan <sup>3</sup>Sony Electronics, Rochester, NY

## **Ultra-High-Speed Wireline**

Session Chair: Amir Amirkhany, Samsung Electronics, San Jose, CA Session Co-Chair: Andrew Joy, Marvell, Northampton, United Kingdom

1:30 PM

# 6.1 A 112Gb/s PAM-4 Long-Reach Wireline Transceiver Using a 36-Way S1 Time-Interleaved SAR-ADC and Inverter-Based RX Analog Front-End in 7nm FinFET

J. Im<sup>1</sup>, K. Zheng<sup>1</sup>, A. Chou<sup>1</sup>, L. Zhou<sup>1</sup>, J. W. Kim<sup>1</sup>, S. Chen<sup>1</sup>, Y. Wang<sup>2</sup>, H-W. Hung<sup>2</sup>, K. Tan<sup>2</sup>, W. Lin<sup>1</sup>, A. Roldan<sup>1</sup>, D. Carey<sup>3</sup>, I. Chlis<sup>3</sup>, R. Casey<sup>3</sup>, A. Bekele<sup>1</sup>, Y. Cao<sup>1</sup>, D. Mahashin<sup>1</sup>, H. Ahn<sup>1</sup>, H. Zhang<sup>1</sup>, Y. Frans<sup>1</sup>, K. Chang<sup>1</sup> <sup>1</sup>Xilinx, San Jose, CA: <sup>2</sup>Xilinx, Singapore; <sup>3</sup>Xilinx, Cork, Ireland

2:00 PM

#### 6.2 A 460mW 112Gb/s DSP-Based Transceiver with 38dB Loss Compensation for Next-Generation Data Centers in 7nm FinFET Technology

T. Ali\*<sup>1</sup>, E. Chen\*<sup>1</sup>, H. Park\*<sup>1</sup>, R. Yousry\*<sup>1</sup>, Y-M. Ying<sup>1</sup>, M. Abdullatif<sup>1</sup>, M. Gandara<sup>1</sup>, C-C. Liu<sup>2</sup>, P-S. Weng<sup>2</sup>, H-S. Chen<sup>2</sup>, M. Elbadry<sup>1</sup>, Q. Nehal<sup>1</sup>, K-H. Tsai<sup>2</sup>, K. Tan<sup>2</sup>, Y-C. Huang<sup>2</sup>, C-H. Tsai<sup>2</sup>, Y. Chang<sup>2</sup>, Y-H. Tung<sup>2</sup> \*Equally-Credited Authors (ECAs), <sup>1</sup>MediaTek, Irvine, CA; <sup>2</sup>MediaTek, Hsinchu, Taiwan

2:30 PM

## 6.3 A 10-to-112Gb/s DSP-DAC-Based Transmitter with 1.2V $_{\rm ppd}$ Output Swing DS1 in 7nm FinFET

E. Groen<sup>1</sup>, C. Boecker<sup>1</sup>, M. Hossain<sup>2</sup>, R. Vu<sup>1</sup>, S. Vamvakos<sup>1</sup>, H. Lin<sup>1</sup>, S. Li<sup>1</sup>, M. van Ierssel<sup>3</sup>, P. Choudhary<sup>1</sup>, N. Wang<sup>1</sup>, M. Shibata<sup>3</sup>, M. H. Taghavi<sup>3</sup>, N. Nguyen<sup>1,4</sup>, S. Desai<sup>1</sup>

<sup>1</sup>Rambus, Sunnyvale, CA; <sup>2</sup>University of Alberta, Edmonton, Canada <sup>3</sup>Rambus, Toronto, Canada; <sup>4</sup>San Jose State University, San Jose

Break 3:00 PM

#### 3:15 PM

#### 6.4 A 56Gb/s 7.7mW/Gb/s PAM-4 Wireline Transceiver in 10nm FinFET Using MM-CDR-Based ADC Timing Skew Control and Low-Power DSP with Approximate Multiplier

B-J. Yoo, D-H. Lim, H. Pang, J-H. Lee, S-Y. Baek, N. Kim, D-H. Choi, Y-H. Choi, H. Yang, T. Yoon, S-H. Chu, K. Kim, W. Jung, B-K. Kim, J. Lee, G. Kang, S-H. Park, M. Choi, J. Shin, Samsung Electronics, Hwaseong, Korea

#### 3:45 PM

6.5 A 6.4-to-32Gb/s 0.96pJ/b Referenceless CDR Employing ML-Inspired Stochastic Phase-Frequency Detection Technique in 40nm CMOS K. Park. M. Shim. H-G. Ko. D-K. Jeong. Seoul National University. Seoul. Korea

4:15 PM

#### 6.6 Reference-Noise Compensation Scheme for Single-Ended Package-to-Package Links

X. Chen<sup>1</sup>, N. Nedovic<sup>1</sup>, S. G. Tell<sup>2</sup>, S. S. Kudva<sup>1</sup>, B. Zimmer<sup>1</sup>, T. H. Greer<sup>2</sup>, J. W. Poulton<sup>2</sup>, S. Song<sup>1</sup>, W. J. Turner<sup>2</sup>, J. M. Wilson<sup>2</sup>, C. T. Gray<sup>2</sup> <sup>1</sup>NVIDIA, Santa Clara, CA; <sup>2</sup>NVIDIA, Durham, NC

4:45 PM

## 6.7 An 8Gb/s/µm FFE-Combined Crosstalk-Cancellation Scheme for HBM on Silicon Interposer with 3D-Staggered Channels

H-G. Ko, S. Shin, J. Oh, K. Park, D-K. Jeong, Seoul National University, Seoul, Korea

5:00 PM

## 6.8 A 100Gb/s NRZ Transmitter with 8-Tap FFE Using a 7b DAC in 40nm CMOS

*P-J. Peng<sup>1</sup>, S-T. Lai<sup>1</sup>, W-H. Wang<sup>1</sup>, C-W. Lin<sup>1</sup>, W-C. Huang<sup>1</sup>, T. Shih<sup>2</sup>* <sup>1</sup>Yuan Ze University, Taoyuan, Taiwan; <sup>2</sup>Teletrx, Taipei, Taiwan

## Demonstration Session 1, Monday February 17th, 5:00-7:00 PM

This year, the Demonstration Session extending in selected regular papers, both Academic and Industrial, will take place on Monday February 17<sup>th</sup>, and Tuesday February 18<sup>th</sup>, from 5 pm until 7 pm in the Golden Gate Hall. These demonstrations will feature real-life applications made possible by new ICs presented at ISSCC 2020, as noted by the symbol **DS1**

- 2.1 Zen 2: The AMD 7nm Energy-Efficient High-Performance x86-64 Microprocessor Core

- 3.1 An Integrated BAW Oscillator with <±30ppm Frequency Stability Over Temperature, Package Stress, and Aging Suitable for High-Volume Production

- 3.3 A 0.51nW 32kHz Crystal Oscillator Achieving 2ppb Allan Deviation Floor Using High-Energy-to-Noise-Ratio Pulse Injection

- 4.7 A Single-Antenna W-Band FMCW Radar Front-End Utilizing Adaptive Leakage Cancellation

- 4.8 A Terahertz FMCW Comb Radar in 65nm CMOS with 100GHz Bandwidth

- 5.1 A 240×192Pixel 10fps 70klux 225m-Range Automotive LiDAR SoC Using a 40ch 0.0036mm<sup>2</sup> Voltage/Time Dual-Data-Converter-Based AFE

- 5.2 A 1200×900 6µm 450fps Geiger-Mode Vertical Avalanche Photodiodes CMOS Image Sensor for a 250m Time-of-Flight Ranging System Using Direct-Indirect-Mixed Frame Synthesis with Configurable-Depth-Resolution Down to 10cm

- 5.3 An Up-to-1400nm 500MHz Demodulated Time-of-Flight Image Sensor on a Ge-on-Si Platform

- 5.4 A Dynamic Pseudo 4-Tap CMOS Time-of-Flight Image Sensor with Motion Artifact Suppression and Background Light Cancelling Over 120klux

- 5.10 A 1280×720 Back-Illuminated Stacked Temporal Contrast Event-Based Vision Sensor with 4.86µm Pixels, 1.066GEPS Readout, Programmable Event-Rate Controller and Compressive Data-Formatting Pipeline

- 6.1 A 112Gb/s PAM-4 Long-Reach Wireline Transceiver Using a 36-Way Time-Interleaved SAR-ADC and Inverter-Based RX Analog Front-End in 7nm FinFET

- 6.2 A 460mW 112Gb/s DSP-Based Transceiver with 38dB Loss Compensation for Next-Generation Data Centers in 7nm FinFET Technology

- 6.3 A 10-to-112Gb/s DSP-DAC-Based Transmitter with 1.2V<sub>ppd</sub> Output Swing in 7nm FinFET

- 24.6 An Instantaneously Broadband Ultra-Compact Highly Linear PA with Compensated Distributed-Balun Output Network Achieving >17.8dBm  $P_{\rm ref}$  and >36.6% PAE<sub>Pref</sub> over 24 to 40GHz and Continuously Supporting 64-/256-QAM 5G NR Signals over 24 to 42GHz

- 28.3 A 5.2Mpixel 88.4dB-DR 12in CMOS X-Ray Detector with 16b Column-Parallel Continuous-Time  $\Delta\Sigma$  ADCs

- 28.4 A CMOS Multimodality In-Pixel Electrochemical and Impedance Cellular Sensing Array for Massively Paralleled Synthetic Excelectrogen Characterization

- 29.3 Non-Magnetic 0.18µm SOI Circulator with Multi-Watt Power Handling Based on Switched-Capacitor Clock Boosting

- 29.5 Sub-THz CMOS Molecular Clock with 43ppt Long-Term Stability Using High-Order Rotational Transition Probing and Slot-Array Couplers

- 30.3 A SAW-Less NB-IoT RF Transceiver with Hybrid Polar and On-Chip Switching PA Supporting Power Class 3 Multi-Tone Transmission

- 30.6 A Low-Power BLE Transceiver with Support for Phase-Based Ranging, Featuring 5µs PLL Locking Time and 5.3ms Ranging Time, Enabled by Staircase-Chirp PLL with Sticky-Lock Channel-Switching

- 34.1 A 64×64 Implantable Real-Time Single-Charged-Particle Radiation Detector for Cancer Therapy

- 34.2 1225-Channel Localized Temperature-Regulated Neuromorphic Retinal-Prosthesis SoC with 56.3nW/Channel Image Processor

- 34.6 EEG Dust: A BCC-Based Wireless Concurrent Recording/Transmitting Concentric Electrode

### **EE3: Industry Showcase**

| Session Chair:    | Kush Gulati, | Omni Design, Milpitas, CA   |

|-------------------|--------------|-----------------------------|

| Session Co-Chair: | Alice Wang,  | Everactive, Santa Clara, CA |

Industry Showcase Committee:

Matteo Bassi, Infineon Technologies AG, Villach, Austria Tom Burd, Advanced Micro Devices, Santa Clara, CA Alison Burdett, Sensium Healthcare, Oxford, United Kingdom Vivek De, Intel, Hillsboro, OR Yohan Frans, Xilinx, San Jose, CA Nagendra Krishnapura, Indian Institute of Technology, Chennai, India Sonia Leon, Intel, Santa Clara, CA Yan Li, Western Digital, Milpitas, CA Patrick Mercier, University of California, San Diego, CA James Myers, ARM, Cambridge, United Kingdom Mijung Noh, Samsung Electronics, Gyeonggi-do, Korea Phillip Restle, IBM T.J. Watson, Yorktown Heights, NY Naveen Verma, Princeton University, Princeton, NJ Long Yan, Samsung Electronics, Gyeonggi-do, Korea Wookyeong Jeong, Samsung Electronics, Gyeonggi-do, Korea

ISSCC will hold a plenary Industry Showcase event on the evening of Monday, February 17th, which will highlight how advances in silicon circuits, SoCs and systems are fueling the most innovative industrial applications and products of the future. Following the recognized role of ISSCC as the foremost global forum for advances in solid-state circuits and systems-on-chip (SoCs), the goal of this event will be to highlight the role of silicon in the creation of novel products. It will feature short presentations as well as interactive demonstrations where attendees can have a hands-on experience with each featured innovation. The featured presentations were chosen through a nomination and voting process by members of the Industry Showcase Committee and represent an exciting introduction to the next generation of applications and products enabled by the sustained evolution of solid-state integrated circuits.

#### Amongst those participating will be:

- Intel (Lakefield: Hybrid Computing with 3D silicon integration)

- Wiliot (Low-Cost Bluetooth Based Sensor Tags for IoT)

- IBM (IBM Z15 A 12 Core 5.2GHz Microprocessor)

- Butterfly Network (Handheld Whole-Body Imager with Ultrasound-on-Chip)

- Weebit Nano (Spiking Neural Network using ReRAM)

- Samsung Semiconductor (Motion-resilient VGA Time-of-Flight Image Sensor)

- Samsung Electronics (A 1/1.33-inch 108MP CMOS Image Sensor with 0.8µm Unit Pixels)